博瑞先进 ASMPT :高速SiP贴装的核心解决方案

2025-08-04

随着智能化趋势的加速发展,电子产品正朝着更小体积、更高性能的方向不断演进,系统级封装(SiP)逐渐成为实现这一趋势的关键技术。它通过在单一封装中集成IC芯片与SMT元器件,有效提升系统性能,同时显著缩小产品尺寸,已成为先进封装的关键路径之一。

然而,面对复杂的封装结构和日益增长的性能要求,传统SiP产线通常需要分别完成SMT贴装与芯片键合两道工序,设备类型多、操作复杂、流程割裂,不仅增加生产成本,也限制了产线的灵活性与响应速度。

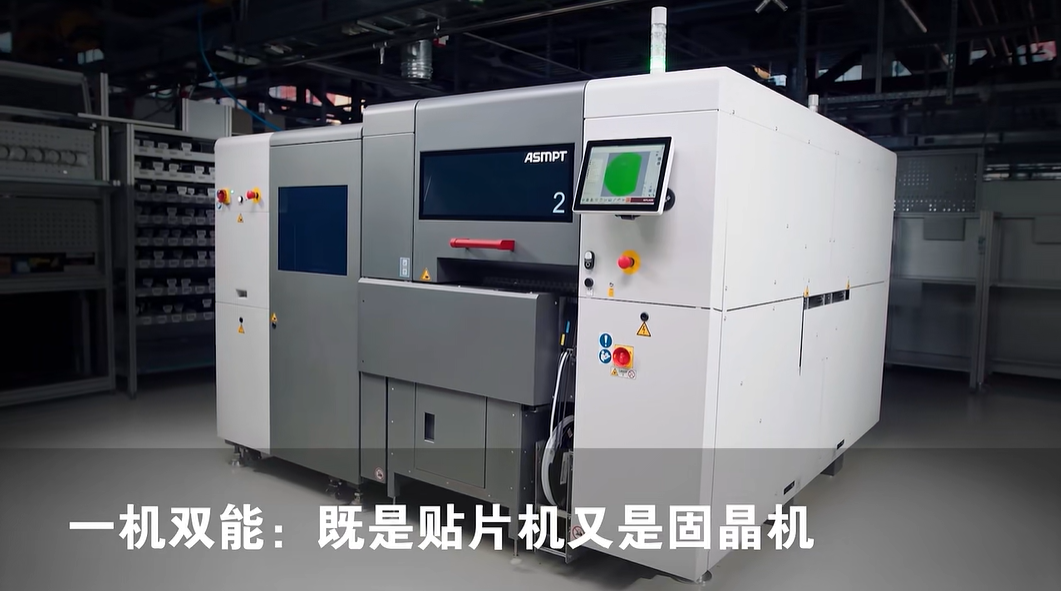

为此,ASMPT推出SIPLACE CA2,将SMT贴装与晶圆芯片贴装整合于一台设备之中,打破传统分段式流程,真正实现“一台机器可以处理两种工艺”,为SiP封装量产提供了更高效、更灵活、更具前瞻性的解决方案。

一台机器处理两种工艺

SIPLACE CA2将SMT与半导体贴装流程融合为一个统一工序,可同时处理卷带SMD元件与直接取自晶圆的裸芯片。其贴装速度高达每小时50,000个芯片或76,000个SMD,精度达10 μm @ 3σ,大幅提升产线柔性、产能与良率,特别适用于各种高速SiP生产应用场景。

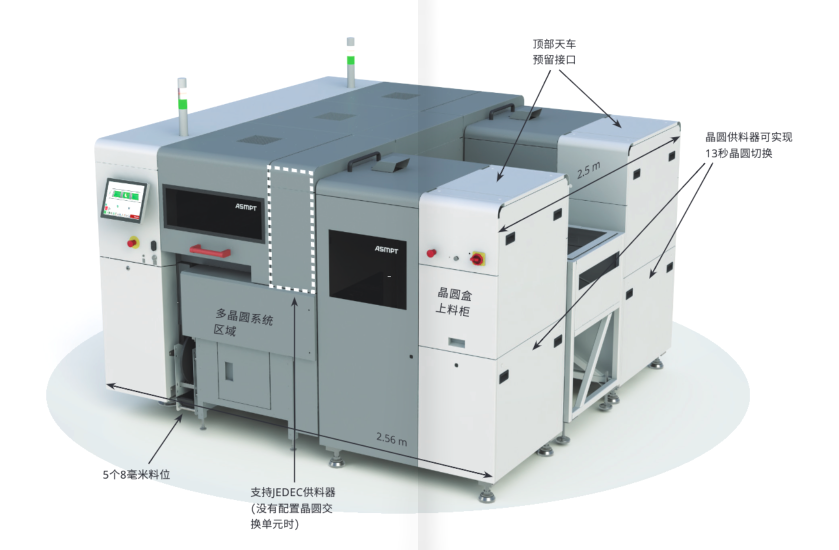

SIPLACE CA2不仅支持一机多任务,也节省了原本需多设备协同的空间和人力成本。高度自动化的芯片缓冲系统可在贴装头作业时同步预取芯片,实现晶圆取片与贴装的并行处理,让芯片处理效率接近传统SMT节拍,同时大幅减少生产瓶颈与换线等待。

从芯片到工厂的全流程智能化

SIPLACE CA2不仅具备高效的晶圆切换能力,最快仅需6.5秒,支持多达50种晶圆,更通过直接处理裸芯片,避免编带过程,帮助客户节省物料成本、减少废料,增强可持续性。

与此同时,SIPLACE技术凭借其“全面的单独裸芯片级追踪能力”,可自动记录每块芯片的拾取位置及其在电路板上的贴装位置,满足高可靠性行业的合规要求。

配合ASMPT的WORKS软件与IPC-CFX、SECS/GEM等标准化接口,SIPLACE CA2可无缝集成至MES与自动化物流系统,助力构建未来智慧工厂。

面向未来封装的战略平台

ASMPT SMT解决方案部高级产品经理 Sylvester Demmel 在总结SIPLACE CA2的战略意义时表示:“SIPLACE CA2 集SiP时代的关键能力于一身,开辟了先进封装的新领域。”

通过将SMT与芯片贴装的流程融合到单一工艺,SIPLACE CA2不仅帮助客户应对先进封装的挑战,更为电子制造商开拓了新的市场机会和客户群体,在提升产能与质量的同时有效降低运营成本,构筑全新竞争优势。

SIPLACE CA2是ASMPT在先进封装与智能制造领域持续技术积累的结晶。它不仅是一次设备升级,更是一种全新制造理念的体现——聚焦效率、绿色与智能,助力客户以更快节奏、更高质量响应技术演进。

在这个系统级封装加速变革的时代,SIPLACE CA2让“未来封装”的目标不再遥远。

最新新闻